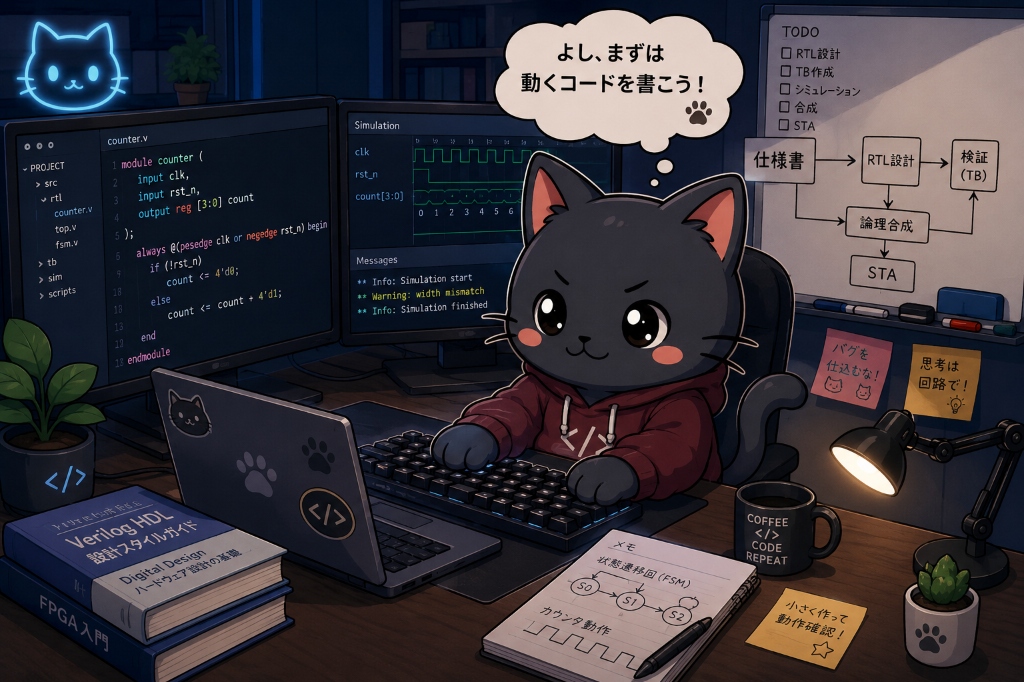

ようこそ、もふねこのHDL実験ノートへ

Verilog-HDLで回路を書きながら、一緒に実験しましょう。

論理回路の基礎から、シミュレーション、論理合成まで。

うまくいかなくても大丈夫。それも実験のうちです。

Verilog-HDLで回路を書きながら、一緒に実験しましょう。

論理回路の基礎から、シミュレーション、論理合成まで。

うまくいかなくても大丈夫。それも実験のうちです。

「HDLとかVerilogって難しそう…」って思った?大丈夫、最初は誰でもそうにゃ!🐾

このノートは「まずはコピペで動かして、波形を見る」ところから始めるよ。分厚い教科書を読む前に、まずは一緒に手を動かして実感してみよう!

いきなり全部読まなくてOK!まずはこの3つの記事で「回路が動く楽しさ」を体験してね。

慣れてきたら、自分のペースで興味のあるノートを読んでみてね。

AND/OR/NOT から始まる回路の世界。Verilogの前に押さえておく基礎。

文法ノートmodule・always・assign など、Verilogの基本文法を手を動かして学ぶ。

回路ノートゲート・FF・カウンタ・ステートマシンを実際にVerilogで記述する。

テクニックノート記述順序の落とし穴、ラッチ生成の原因など、実務でよく詰まるポイントを解説。

合成ノート制約条件・タイミング・スクリプト。論理合成ツールの使い方を体系的に学ぶ。

検証ノートテストベンチの書き方からシステムタスクまで。回路の動作確認を徹底的に。

サイドバーからはいつでも任意のページに移動できます。カテゴリ名をクリックすると、リストを折りたたむこともできます。